ARM架构-keil_gcc_Makefile

2024年9月 · 预计阅读时间: 7 分钟

1.keil 等 IDE 的背后#

IDE 指集成开发环境(Integrated Development Environment)。 我们开发 STM32F103 等单片机程序时使用是 keil 就是一种 IDE。

使用 IDE,很容易操作,点点鼠标就可完成:

- 添加文件

- 指定文件路径(头文件路径、库文件路径)

- 指定链接库

- 编译、链接

- 下载、调试

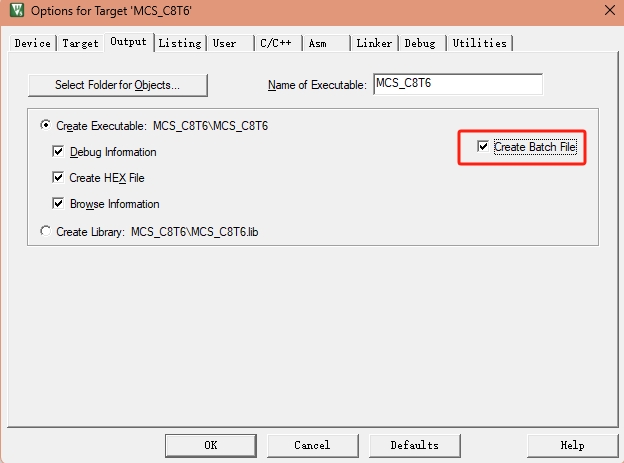

1.1 IDE 背后是命令行#

在 keil 中勾选批处理文件生成选项,就可以得到 windows 下的命令行脚本文件。

注意

- 使用 GitBash 执行命令的话

由于 GitBash 采用类似 Linux 的文件路径表示方法(比如

/d/abc,而非d:\abc),命令行中 windows 格式的路径名要加上双引号,比如".\objects\main.o" - 使用 dos 命令行执行命令的话 不需要加双引号

- 使用 GitBash 执行命令的话

由于 GitBash 采用类似 Linux 的文件路径表示方法(比如

在某个 Keil 工程所在目录下,打开 Git Bash:

doc_and_source_for_mcu_mpu\STM32MF103\source\02_录制视频时现场编写的源码\01_led_c编译 main.c 执行命令:

编译 start.S 执行命令:

链接 执行命令:

1.2 有两套主要的编译器#

armcc

- ARM 公司的编译器

- keil 使用的就是 armcc

gcc

- GNU 工具链

- Linux 等开源软件经常使用 gcc

后面以 GNU 工具链为例讲解,所涉及的知识可以平移到 armcc 上。

1.3 几个问题(头文件、库文件、源文件)#

头文件在哪?

库文件在哪?库文件是哪个?

源文件有哪些?

源文件怎么编译?可以指定编译参数吗?

多个源文件怎么链接成一个可执行程序?

有 a.c, b.c, c.c,我只修改了 a.c,就只需要编译 a.c,然后在链接:怎么做到的?

这些问题需要详细了解编译过程了

回答:

头文件来自:

1)可以自己指定

-I <头文件目录>2)系统目录:工具链里的某个 include 目录

库文件在哪里?库文件是哪个?

1)系统目录

系统目录在哪?工具链里的某个 lib 目录

怎么确定?

2)可以不使用系统 lib 目录吗?可以,编译时指定参数

-nostdlib3)可以自己指定库文件目录

4)指定库文件

静态库文件:通常以

.a结尾,保存的是目标文件的集合,编译时直接链接到可执行文件。动态库文件:通常以

.so结尾(Linux 系统),运行时加载,编译时只保留符号信息。源文件有哪些?

源文件是以

.c为后缀的 C 语言文件源文件怎么编译?可以指定编译参数吗?

见 3.gcc 的使用方法

多个源文件怎么链接成一个可执行程序?

编译多个源文件后,生 gcc -c a.c 成的目标文件(

.o文件)可以通过 GCC 链接成一个可执行文件。如果涉及外部库,还需要用-l和-L指定库文件。有 a.c, b.c, c.c,我只修改了 a.c,就只需要编译 a.c,然后在链接:怎么做到的?

如果只修改了

a.c,可以单独编译a.c,然后链接其他已编译的目标文件。具体示例:使用 gcc 链接会添加一些默认的文件,而 LD 只会链接指定的文件

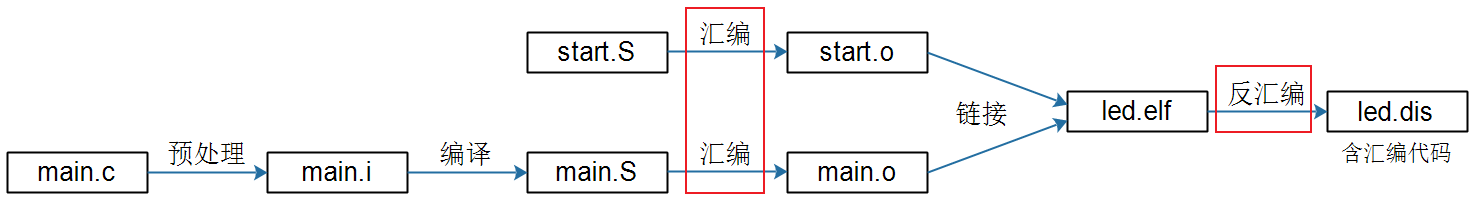

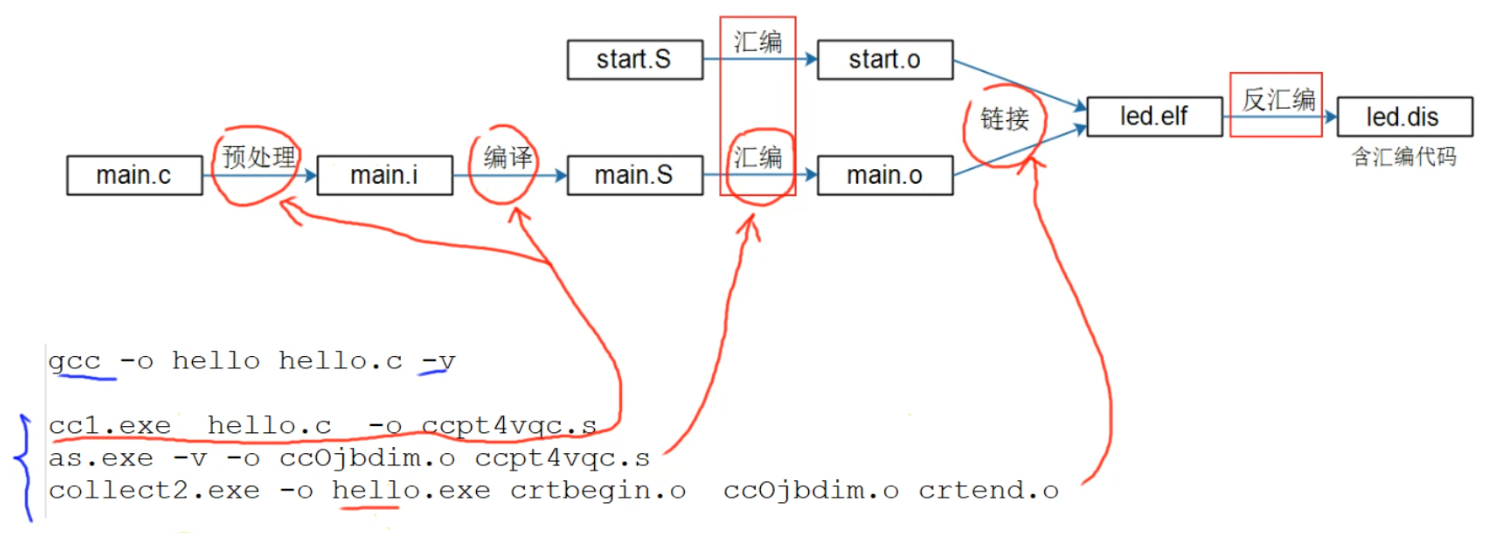

2.gcc 编译过程详解#

我们经常使用“编译”泛指下面的 4 个步骤之一,甚至有时候会囊括这四个步骤。

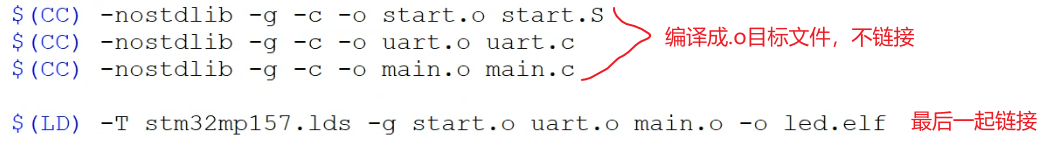

上面一条命令可以分为下图三条命令,对于上面四个步骤:

最常用的方法是

这样如果有一个文件修改了,只需要重新编译那一个文件,然后再链接就可以了,不需要重新编译所有文件。

那么问题又来了,怎么知道哪些文件被更新了/被修改了?

比较时间:比较 .o 和 .c 的时间,如果.c 的时间比 .o 的时间更加新的话,就表明 .c 被修改了。比较 output 和 所有.o 文件 的时间,如果.o 文件的时间比 output 更加新的话,就表明应该重新生成 output。Makefile 就是这样做的。

2.1 预处理阶段#

展开头文件、替换宏定义、处理一些预处理指令(例如#ifdef)

2.2 编译#

词法、语法检查,生成汇编文件

2.3 汇编#

生成二进制文件,即目标文件

2.4 链接#

把所有的目标文件和库文件链接成一个可执行程序

3.gcc 的使用方法#

| 选项 | 功能 |

|---|---|

-v | 查看 gcc 编译器的版本,显示 gcc 执行时的详细过程 |

-o <file> | 指定输出文件名为 file,这个名称不能跟源文件名同名 |

-E | 只预处理,不会编译、汇编、链接 t |

-S | 只编译,不会汇编、链接 |

-c | 编译和汇编,不会链接 |

4.Makefile#

4.1 Makefile 的规则#

makefie 最基本的语法是规则,规则:

当“依赖”比“目标”新,或还没有"目标",就执行它们下面的命令。

示例如下:

第一次执行 make:(三条命令都执行)

- 先执行第一个目标和依赖:a.o 依赖 a.c

- 执行下面的命令

gcc -c -o a.o a.c生成 a.o - 然后发现 b.o 也没有,同理执行

gcc -c -o b.o b.c - 最后再执行

gcc -o test a.o b.o,生成 test

修改 a.c 之后,再执行 make:(执行两条命令)

- 执行第一个目标和依赖:a.o 依赖 a.c

- 发现 a.c 比 a.o 更新,执行下面的命令

gcc -c -o a.o a.c生成 a.o - b.o 依赖 b.c,但并没有更新,不会重新生成

- 最后同样执行

gcc -o test a.o b.o,生成 test

可以使用touch b.c修改以 b.c 的时间为当前时间,重新 make:

4.2 Makefile 的语法#

本节我们只是简单的讲解 Makefile 的语法,如果想比较深入

学习 Makefile 的话可以:

- a. 百度搜 "gnu make 于凤昌"。

- b. 查看官方文档: http://www.gnu.org/software/make/manual/

1)通配符#

假如一个目标文件所依赖的依赖文件很多,那样岂不是我们要写很多规则,这显然是不合乎常理的。

我们可以使用通配符,来解决这些问题。

我们对上节程序进行修改代码如下:

%.o:表示所用的.o 文件

%.c:表示所有的.c 文件

$@:表示目标

$\<:表示第 1 个依赖文件

$\^:表示所有依赖文件

2)假想目标: .PHONY#

1.我们想清除文件,我们在 Makefile 的结尾添加如下代码就可以了:

1)执行 make :生成第一个可执行文件。

2)执行 make clean : 清除所有文件,即执行: rm \*.o test。

make 后面可以带上目标名,也可以不带,如果不带目标名的话它就想生成第一个规则里面的第一个目标。

2.使用 Makefile

执行:make [目标] 也可以不跟目标名,若无目标默认第一个目标。我们直接执行 make 的时候,会在 makefile 里面找到第一个目标然后执行下面的指令生成第一个目标。当我们执行 make clean 的时候,就会在 Makefile 里面找到 clean 这个目标,然后执行里面的命令,这个写法有些问题,原因是我们的目录里面没有 clean 这个文件,这个规则执行的条件成立,他就会执行下面的命令来删除文件。

如果:该目录下面有名为 clean 文件怎么办呢?

我们在该目录下创建一个名为 “clean” 的文件,然后重新执行:make 然后 make clean,结果(会有下面的提示:):

它根本没有执行我们的删除操作,这是为什么呢?

我们之前说,一个规则能过执行的条件:

1)目标文件不存在 2)依赖文件比目标新

现在我们的目录里面有名为“clean”的文件,目标文件是有的,并且没有

依赖文件,没有办法判断依赖文件的时间。这种写法会导致:有同名的"clean"文件时,就没有办法执行 make clean 操作。

解决办法:我们需要把目标定义为假象目标,用关键子 PHONY

然后在 Makfile 结尾添加.PHONY: clean 语句,重新执行:make clean,就会执行删除操作。

3)变量#

实例:

执行:

结果:

分析:

- A := $(C):

A 为即使变量,在定义时即确定,由于刚开始 C 的值为空,所以 A 的值也为空。

B = $(C): B 为延时变量,只有使用到时它的值才确定,当执行 make 时,会解析 Makefile 里面的所用变量,所以先解析 C= abc,然后解析 C += 123,此时,C = abc 123,当执行:\@echo B = $(B) B 的值为 abc 123。

D ?= weidongshan:

D 变量在前面没有定义,所以 D 的值为 weidongshan,如果在前面添加 D = 100ask,最后 D 的值为 100ask。

我们还可以通过命令行存入变量的值 例如:

执行:make D=123456 里面的 D ?= weidongshan 这句话就不起作用了。

结果:

4.3 Makefile 函数#

makefile 里面可以包含很多函数,这些函数都是 make 本身实现的,下面我们来几个常用的函数。引用一个函数用“$”。

1)函数 foreach#

函数 foreach 语法如下:

前两个参数,‘var’和‘list’,将首先扩展,注意最后一个参数 ‘text’ 此时不扩展;接着,对每一个 ‘list’ 扩展产生的字,将用来为 ‘var’ 扩展后命名的变量赋值;然后 ‘text’ 引用该变量扩展;因此它每次扩展都不相同。结果是由空格隔开的 ‘text’。在 ‘list’ 中多次扩展的字组成的新的 ‘list’。‘text’ 多次扩展的字串联起来,字与字之间由空格隔开,如此就产生了函数 foreach 的返回值。

实例:

结果:

2)函数 filter/filter-out#

语法如下:

实例:

结果:

3)函数 Wildcard#

语法如下:

这个函数 wildcard 会以 pattern 这个格式,去寻找存在的文件,返回存在文件的名字。

实例:

在该目录下创建三个文件:a.c b.c c.c

结果:

我们也可以用 wildcard 函数来判断,真实存在的文件

实例:

结果:

4)函数 patsubst#

语法如下:

patsubst 函数是从 var 变量里面取出每一个值,如果这个符合 pattern 格式,把它替换成 replacement 格式,

实例:

结果:

4.4 完整示例#

1)为每个.c 文件添加.h 文件#

怎么为每个.c 文件添加.h 文件呢?对于内核,有几万个文件,不可能为每个文件依次写出其头文件。 因此需要做出改进,让其自动生成头文件依赖,可以参考这篇文章:http://blog.csdn.net/qq1452008/article/details/50855810

2)示例#

修改 Makefile 如下:

首先用 obj 变量将.o 文件放在一块。

- 利用前面讲到的函数,把 obj 里所有文件都变为.%.d 格式,并用变量 dep_files 表示。

- 利用前面介绍的 wildcard 函数,判断 dep_files 是否存在。

- 然后是目标文件 test 依赖所有的.o 文件。

- 如果 dep_files 变量不为空,就将其包含进来。

- 然后就是所有的.o 文件都依赖.c 文件,且通过-MD -MF 生成.d 依赖文件。

- 清理所有的.o 文件和目标文件

- 清理依赖.d 文件。

再添加 CFLAGS,即编译参数。比如加上编译参数-Werror,把所有的警告当成错误。

现在重新 make,发现以前的警告就变成了错误,必须要解决这些错误编译才能进行。在a.c里面声明一下函数:

重新 make,错误就没有了。

除了编译参数-Werror,还可以加上-I 参数,指定头文件路径,-Iinclude 表示当前的 inclue 文件夹下。

此时就可以把 c.c 文件里的#include ".h"改为#include <c.h>,前者表示当前目录,后者表示编译器指定的路径和 GCC 路径。